728x90

Multibit Register and Latches

- 레지스터 : common clock input을 갖는 2개 이상의 flipflop 조합

- ex. 74374 register

- CLK가 rising일 때 1~8D값이 저장

- OE_L이 내부에 tri-state buffer 회로로 1~8Q에 연결, OE_L이 on이 되어야 저장된 signal이 출력

Counter

- 1 - 2 - 3 - ... - 다시 1로 반복하는 sequential circuit

- state diagram이 1개의 cycle로 구성

- m개 state의 counter = modulo-m counter = divide by m counter

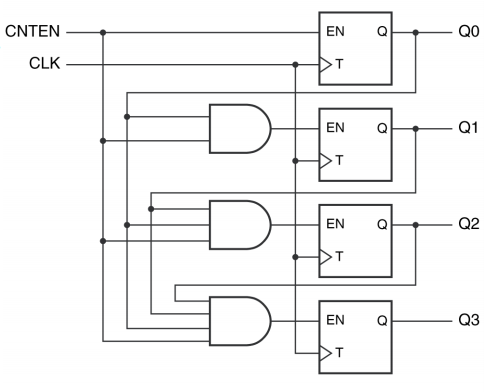

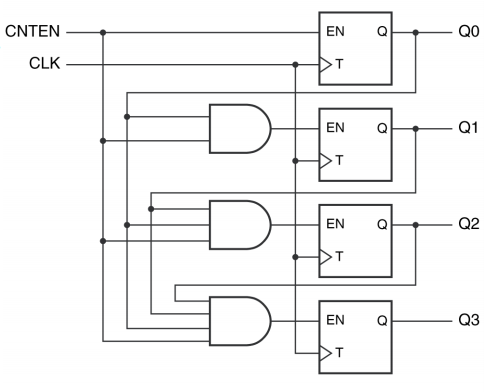

- n-bit binary counter with T flip flop

- n개의 ff로 0 ~ 까지 count 가능

synchronous counter

| a | b | c | d | ||

|---|---|---|---|---|---|

| Q0 | 0 | 1 | 0 | 1 | 0 |

| Q1 en | 0 | 0 | 1 | 0 | 1 |

| Q1 | 0 | 0 | 1 | 1 | 0 |

| Q2 | 0 | 0 | 0 | 0 | 1 |

- Q1 en은 Q0에서의 transition에 의해 시간차를 두고 입력

- 4-bit number abcd=0101일 때, Q0에 C값이 들어갈 때 Q1 en에는 Q0의 b값이 입력

- Q2, Q3 en 역시 Q1, Q2값을 전달받아 동작하므로 각각 시간차를 두고 입력됨

- propagation delay로 인해 자리수가 늘 수록 동작이 느려짐

Synchronous Parallel Binary Counter

- 자리수가 높아질 수록 직전 자리수들의 출력 신호가 누적되어 입력

- And-gate의 pan-in이 증가하므로 low-high 변화 시간이 길어짐 = 동작을 위한 최소 clock에 제한

- 또한 병렬연결에 의해 clock입력의 전류 크기가 커져야 함

-

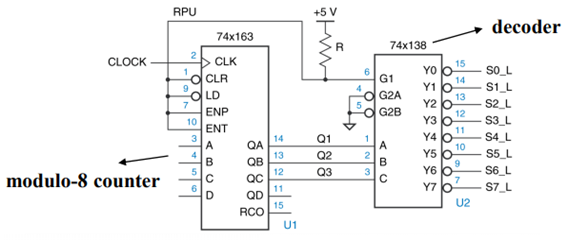

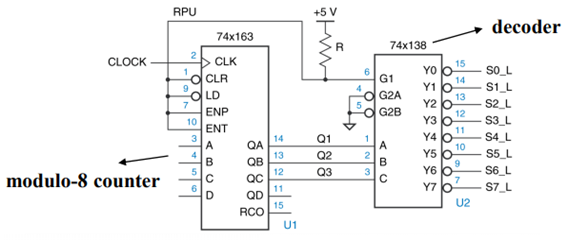

ex. 74163 free running mode

- free running : clock이 입력되면 연속하여 동작

- CLR : low 신호가 입력되면 출력을 바로 0000으로 초기화 (asynchronous)

- LD(Load) : low 신호가 입력되면 A~D에 입력된 신호를 출력 (synchronous)

- 분주 : 주기를 등분으로 나눔

- RCO 신호를 다른 74163의 clock에 연결하면 확장된 counter를 만들 수 있음

- 신호에 저항을 연결하는 이유 : 전류 제한

Decoding Binary Counter States

- counter 출력 신호를 decode

- decoder의 출력 변화로 인해 출력신호에 glitch 발생 : 출력단에 병렬 C를 연결하여 glitch 보상

Other sequence Counter

- 원하는 순서대로 동작하는 카운터

- case. T flip flop

- transition table 작성

- next state와 Toggle input에 대한 K-map을 각각 작성

- 이를 이용하여 회로도 작성

- 오류 발생을 가정 : ex. 오류 발생시 출력을 000으로 초기화

Shift Register

- Shifter(Shift register) : 전달을 목적으로 하는 register

- 컴퓨터 간 통신 (rotate shifter)

- arithmatic shifter : 1bit씩 옮겨서 값을 2배로 곱하거나, 1/2로 나눔

- clock당 n-bit를 움직이는 shifter

- bps : bit-per-second, 초당 전송하는 bit 수

- ex. rising edge shifter, 100Mbps

= 초당 rising edge가 100M개인 clock으로 통신 - 기기 간 데이터 통신을 위해서는 shift register가 필요

- shifter 내 flipflop의 transition time에 의한 제한이 존재하므로 원하는 대로 속도를 증가시킬 수는 없음

- ex. rising edge shifter, 100Mbps

-

Serial-in, Serial-out(SISO) shifter(좌)

- clock 입력 > D FF on, 입력단 D FF 신호는 다음 D FF로 전송

- clock 입력에 따라 순차적으로 다음 FF로 데이터 전송, 출력

- 모든 데이터가 전송되는데 FF 개수만큼의 clock 필요

-

Serial-in, Parallel-out(SIPO) shifter(우)

- 입력 과정은 SISO와 동일 : 모든 데이터가 입력되는데는 FF 개수만큼의 clock 필요

- 데이터 출력은 동시에 이루어짐

- Parallel-in, Serial-out(PISO) shifter

- LOAD/SHIFT

- 1은 LOAD 신호, 0은 SHIFT 신호

- LOAD일 때는 1D-ND까지의 신호가 D FF로 입력

- SHIFT일 때는 LOAD된 신호를 SEROUT으로 순차 출력

- LOAD-LOAD 사이에는 FF 개수만큼의 Clock 필요(입력된 신호를 모두 전송)

- LOAD/SHIFT

- Parallel-in, Parallel-out(PIPO) shifter

- PISO와 다르게 각 FF이 parallel하게 출력

- ex. 74194 Universal Shift Register

- 4bit bidirectional PIPO shifter

- 74194 extension

- CLK, CLR, S0, S1핀은 공통으로 사용

- Q8~Q5, Q4~Q1 74194가 각각 존재할 때,

Q5 출력은 Q4~Q1 74194의 LIN으로,

Q4 출력은 Q8~Q5 74194의 RIN으로 입력 :

left/right shift시 74194 간 신호 전달 - MSB, LSB에만 출력 사용시 PISO shifter로 사용 가능 :

MSB는 Serial Right out, LSB는 Serial Left Serial Out

- 74194 ring counter

- 2진 카운터와 다르게 특정 순서로 움직이지 않고, bit 위치가 순환하면서 이동

- ex. D만 on하고 나머지는 GND한 경우

0001 > 0010 > 0100 > 1000 > 0001 ... - 74194 4-bit 4-state self correcting ring counter

- 74194 ring counter의 경우 중간에 신호 오류가 발생하면 그 오류를 그대로 반영하여 shift함

- LSB를 제외한 나머지를 NOR회로로 연결

- LIN 입력에 Q0~Q2신호가 000일 경우에만 1을 넣어주고, 그 외에는 0을 넣어 일정 clock후 정상신호를 회복하도록 함(최대 3clock 소요)

- Johnson Counter

- n-bit, 2n states

- LSB에 인버터를 연결하여 LIN 신호로 입력

- 0000 입력 기준으로 MSB부터 순서대로 1로 채워짐

- 1111이 되면 MSB부터 순서대로 0으로 채워짐

- Q0~Q3 : 0000 > 1000 > ... > 1111 > 0111 > ... > 0000 > 1000 > ... shift를 반복

- Self Correcting Johnson counter

- 출력 핀 중 일부를 NOR회로로 연결하여 74194 S0단자에 연결

- 오류 발생시 일정 clock이 지난 후 S0에 1 신호가 입력되면 DCBA 신호가 출력되어 신호 정상화

- Linear FeedBack Shift Register Counter

- 개 state를 갖는 카운터(최대 길이)

- n-bit parallel shift register에 대해 정해진 feedback 입력을 XOR연결하여 SERIN단자에 연결

- LFSR with 0 state

- 2n개 state를 갖는 카운터

- LSB를 제외한 출력을 NOR연결하고, LFSR XOR 출력과 XOR하여 all 0 state를 구현

Timing and Synchronization Issue

Clock Skew

- 회로 내 배선 길이가 길어지는 경우 신호 전달에 시간차 발생

- Q1은 정상적인 D FF 동작을 나타내나, D2로의 clock전달이 지연되어 원래 Q2는 0으로 출력되어야 하지만 1로 출력

- Clock skew 방지

- 병렬 신호선 일부에만 buffer 부착시 clock skew 발생

- 모든 신호에 같은 buffer를 부착 (가급적 동일 IC를 통해 연결)

- 선로에 병렬 커패시터를 연결하여 의도적으로 신호전달을 지연시켜 시간차를 맞추는 방법도 존재

Asynchronous Input

- 디지털 시스템의 입력은 대부분 클록과 동기화되지 않은(=언제 입력될 지 모르는) 입력

- synchronizer를 이용하여 clock에 동기화된 입력으로 변환

- 극단적인 noise : clock edge에서 비동기 신호가 유지되지 못하고 순간 변화한 경우는 신호 전달에 오류

- 비동기 신호를 2개의 synchronized state로 나타내고자 할 때 synchronizer 2개를 사용하는 것은 부적절

- 동기화 간 clock delay 존재 = 같은 클락에 다른 응답 가능성

- 동기화 된 하나의 신호를 Combinational Logic을 통해 나누어 출력하는 것이 좋음

728x90