728x90

전류원의 응용

- 일정한 전류(bias)가 통할 때 트랜지스터가 원하는 방식대로 동작

- 공급 전압, 공정, 온도 의존성이 낮은 회로 설계 및 다른 전류원과의 매칭 등 고려 필요

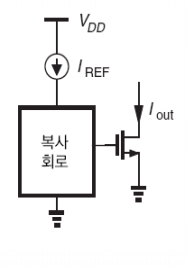

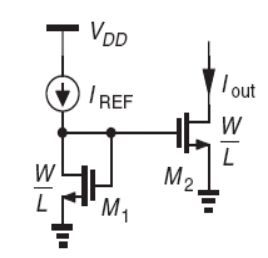

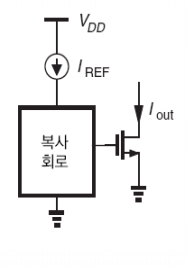

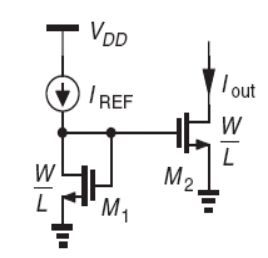

전류 미러

- PVT조건에 대해 엄격한 기준 전류원 설계

- Gate-Drain을 연결한 MOS를 이용하여 Current Mirror 생성

- 큰 Channel-Length를 써야 노이즈 감소, 매칭, 출력 저항 면에서 유리

- 전류 미러 오차 : Channel-Length Effect에 의해 ref와 copy 전류 간 오차 발생

- Cascode 전류미러

- Cascode : 출력 저항(Channel-Length eff.의 역수)의 증폭

- 요구되는 전압이 매우 커짐

- 정확도-헤드룸 trade off

- head-room : 회로가 정상 동작(saturation+gain+current matching) 가능한 DC전압 범위

- 간단한 회로는 큰 헤드룸, 낮은 정확도

- Cascode는 좁은 헤드룹, 높은 정확도

- 저전압 Cascode

- Current Mirroring 대신 하단 Gate를 feedback

- 모든 TR소자가 Saturation되기 위한 적절한 입력 전압 설정 필요

| resistor network | zener diode | MOSFET | |

|---|---|---|---|

| process variation | OK | not good | not good |

| Supply Rejection | poor | good | good |

| Temperature Drift | OK | not good | not good |

- process variation : 공정 수정

- supply rejection : AC성분 감쇠

- temperature drift : 온도에 의한 특성 변경

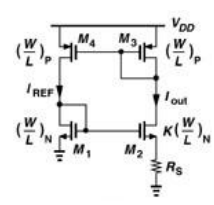

supply independent biasing

- K배 비율을 둔 current mirror 출력단에 저항을 배치하여 통전

- bootstrap : 상호 current mirroring을 통해 전류 변화를 억제

- : 공급 전압에 독립적인 전류(Constant biasing)

- Body effect에 의해 Threshold Voltage에 오차가 발생 - PMOS를 이용하여 source-body를 연결하여 body effect의 제거 가능

- Body effect에 의해 Threshold Voltage에 오차가 발생 - PMOS를 이용하여 source-body를 연결하여 body effect의 제거 가능

- 실 제품 설계시 안정성 있는 제품 제조가 중요 : 오동작(error)의 상당수는 상호 피드백에서 발생

- 기준 전압이 없으므로 Gate단이 On으로 switching되는 과정에서 소자가 통전되지 못할 확률이 존재

- diode를 이용하여 전압차를 비교하여 평형시켜주는 보조 필요

- startup 회로

- 적절한 초기 전압 (PMOS<NMOS)일 때 동작 x

- NMOS 전압이 더 높아질 때 동작

Bandgap Voltage Reference(BGR)

- 실리콘 등 물질의 고유 특성인 bandgap은 불연속적으로 형성

- 물질 자체의 특성이므로 어느 정도 신뢰성이 있음 : Power IC 설계시 Bandgap 특성에 기반한 설계

- BJT 전류식에 기반하므로 BJT 소자를 이용하여 BGR회로 설계

- 온도와 는 (-) 의 관계

- thermal voltage 는 온도와 (+)관계

- 의 합으로 온도의 영향 상쇄 가능

- Negative-Temperature Coefficient(by )

- ,

-

- 의 온도에 대한 의존도는 Bandgap에 dependent

- 일 때 약 -1.5mV/K

- CTAT(compliment-to-absolute-temperature)

- Positive-TC

- 2개의 의 전압 차이를 이용

- (양의 coefficient)

- PTAT(proportional-to-absolute-temperature)라고도 함

- Bandgap reference는 PTAT과 CTAT의 결합이라고도 표현

- Concepture Generation

- 크기가 A, nA인 두 BJT 가정

- 전압 는 Opamp의 virtual short 특성을 이용해 동일하게 설정 가능

- : CTAT+PTAT

- Practical Generation

- 로 설정 : matching 특성을 맞추기 위해

- BJT 크기 특성상 보통 n=15, 7정도를 많이 채택

- n이 클수록 variation 감소

- CMOS공정 시 npn BJT 사용 불가

- lateral BJT(원래 BJT보다는 좋지 못한 특성)을 이용하여 설계

- BCD(Bipolar, CMOS, DMOS) 공정 시 npn 사용 가능

- BGR error

- current mirror, layout의 mismatch

- CMOS 공정의 한계

- Opamp offset

- npn transistor 한계

- BGR Issue

- Supply Dependence : 공급 전압에 대한 출력 전압의 독립성은 충분히 유지 가능

- Startup : cross-reference 회로에 대한 startup 문제의 방지를 위해 diode 등을 이용하여 소자의 이상동작 방지

- Curvature Correlation : 온도, 전류 등에 의해 특성곡선이 변화 - gain 등을 조정하여 보완

728x90