728x90

아날로그 특성

- 아날로그 신호는 매우 작은 크기의 신호 + 간섭(interfere)를 포함

- 신호 처리(증폭기) + 간섭 제거(필터) ( + ADC )

- 핵심 역할은 주로 op-amp가 처리

아날로그 설계의 난점

- 디지털은 속도-전력 trade off관계를 갖는 반면, 아날로그는 속도, 전력, 이득, 정밀도, 잡음 등 고려할 점이 많아짐

- 잡음, 누화(crosstalk), 간섭(interfere)에 매우 민감

- 설계시 Full-Custom과정을 많이 거침 : 시뮬레이션, 모델링이 발전했음에도 실제 동작과의 차이 존재

- IoT, 웨어러블 등 기기를 위한 Analog 회로 설계에 있어서 고성능 저전력, 디지털 회로와의 조합 등 trend 변화

아날로그 회로 설계

- PVT : Process, Voltage, Temperature 요소에 대한 견고한 공정 필요

- Typical - Fast - Slow 3가지를 동작 조건을 고려하여 몬테카를로 시뮬레이션을 이용한 무작위 조건 하에서 정상 동작하는지 확인 필요

CMOS (Compliment MOS)

- 소자 크기, 제조 비용이 매우 작음

- steady 상태의 current는 0에 가깝고, 스위칭 동작 시 전력 소모도 작은 편

- Source-Drain 간 길이, Gate 산화막 두께가 회로에 중요한 역할

Threshold Voltage

- Gate에 충분한 전압 (Threshold Voltage)가 인가되면 Source 전하가 Gate측 경계를 흐르다 Drain으로 이동

- Channel이 형성, MOS가 켜진다 혹은 경계가 반전되었다고 표현

- 문턱 전압 = work function(설계상 조절 x) + 도핑 농도의 함수

- 최근 공정에서는 SVT(Standard Threshold), LVT(Low Threshold), HVT(High Threshold)로 나뉨

- 대기시간이 긴 IOT 등의 경우 누설전류가 작아야 하는 requirement가 있어 HVT소자 사용

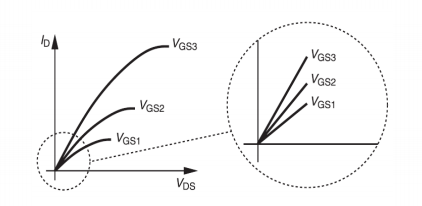

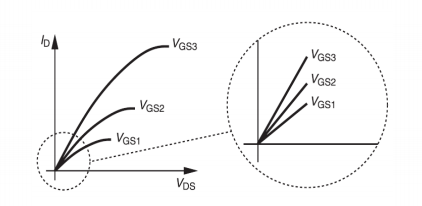

I-V Characteristics

- 일 때 Drain 전류가 최대

- 이보다 작으면 Triode, 크면 Saturation

- 충분히 작은 Drain 영역())에서 MOS소자는 저항과 같이 동작

- Saturation : 가 를 약간 상회할 때, 채널이 pinch-off됨

- Drain 전압이 늘 수록 채널의 depletion region이 늘어남

- 이로 인해 pinch-off된 영역이 더 커짐 = 채널 길이는 짧아진 효과(Channel-Length Modulation)

Transconductance

- 설계 = 사양을 만족하기 위해 parameter를 정하는 것

- MOS 설계 parameter인 전류, 전압, size 중 size or 전류 조정이 상대적으로 쉬움

(는 거의 고정값, 는 bias 문제로 조정 폭 제한)

- 고정된 size(W/L)에 대해서 은 루트 관계

- 고정된 에 대해 은 역수 관계 형성

- 비용 감축을 위한 size 조절 vs 사용전력 감축을 위한 조절

- Body effect(Backgate Effect)

- Source-Body(Substrate) 간 전압차에 의해 가 증가

- 입-출력 전압의 왜곡을 유발

- Channel-Length Modulation

- Drain 전압 변화에 의해 채널 길이가 짧아지는 효과가 발생하여 가 증가

- 채널 길이가 긴 경우 Channel-Length Modulation의 영향이 적음 : 아날로그 증폭기 설계시 공정이 미세해져도 면적 크기는 대체로 일정한 편

- subthreshold conduction

- 실제 MOS소자 동작은 문턱 전압 이하에서도 약한 inversion layer 형성

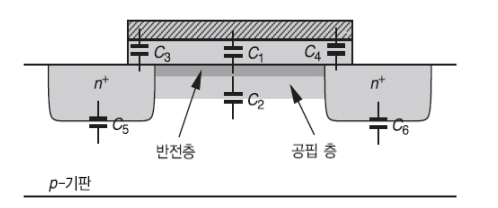

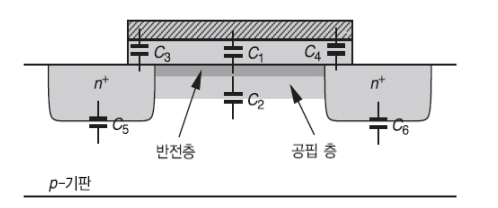

MOS Capacitance

- Metal-Oxide-Semiconductor의 소자 특성에 의해 전기용량 영역이 자연스럽게 형성

- MOS 크기가 증가(W, L 증가) 시 Gate 측의 Capacitance가 증가하는 부작용이 존재

- gate switching시 필요한 에너지(Switch Loss), 전환 시간 증가

- Source, Drain을 GND하고 Gate에 전압 인가시 Capacitor처럼 동작

CMOS Analog Basic

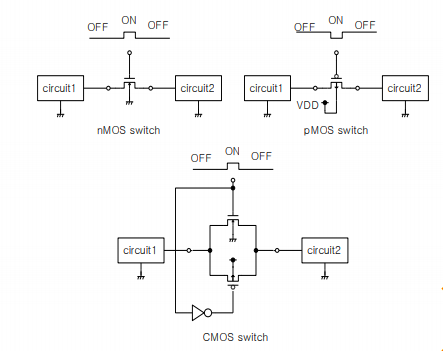

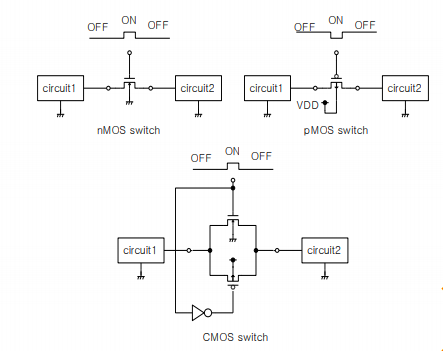

MOS의 스위치 특성

- NMOS : high on - 저전압 통과

- PMOS : low on - 고전압 통과

- CMOS : high on - 신호 범위가 넓어야 하는 경우 활용

- 입력 전압에 의해 on 상태의 저항값이 바뀌는 문제

- 전압에 따라 Triode-saturation 상태가 바뀌기 때문에 발생

- NMOS, PMOS를 병렬로 구성하면 입력전압에 독립적인 회로 구성 가능

- N, PMOS의 mobility와 크기가 각각 동일할 때 입력 전압에 동일한 회로 구성 가능

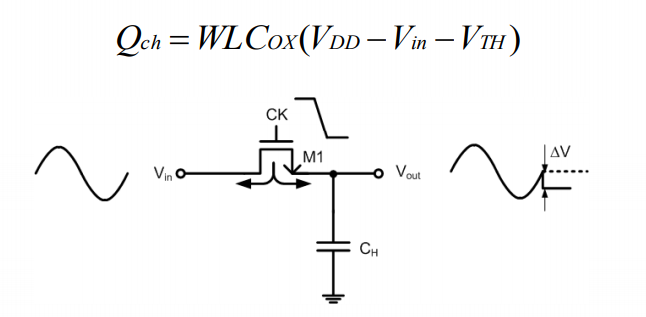

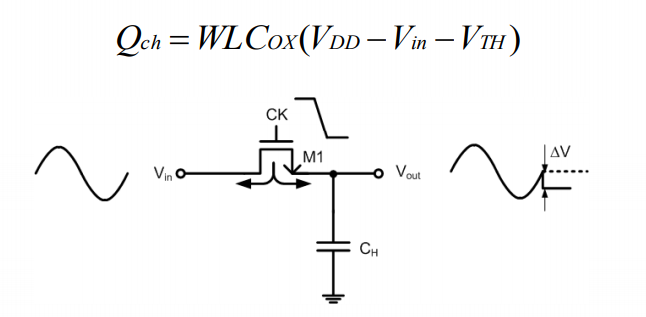

Channel Charge Injection

- MOS 회로가 On > OFF로 바뀔 때 C의 방전 특성에 의한 Channel Charge에 의해 의도하지 않은 순간적인 전압 변화 발생

- 이상적으로는 입력전압에 비례하여 출력전압이 나와야 하지만, Channel Charge Injection에 의해 offset을 갖는 출력 발생

- Channel Length를 줄이고, MOS 회로의 Capacitor 를 줄여 보완 가능

- Clock feedthrough

- MOS의 C특성에 의해 gate를 통하는 switch on/off 신호가 출력전압에 전달되는 현상

- 소자 크기(W)를 줄이거나,

- kt/C noise

- 온도에 비례하고, 정전용량에 반비례하는 노이즈 발생

- 아날로그 회로의 샘플링 노이즈 감소를 위해서는 회로 내 C 크기를 증가

- Charge Injection 방지

- 더미 회로를 하나 추가하여 Charge Injection을 방지할 수 있음

- CMOS 사용시 NMOS는 전자 / PMOS는 정공이 변화하므로 다소 완화 가능

- Differential Sampling : ADC 등의 경우 2개 MOS 회로로 구성된 차동 회로를 이용하여 Charge Injection을 다소 완화

- 더미 회로를 하나 추가하여 Charge Injection을 방지할 수 있음

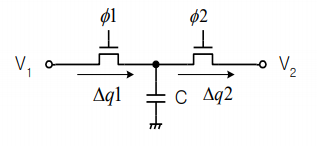

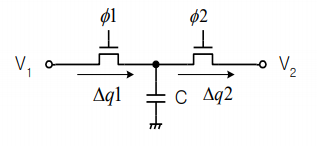

Switch Capacitor Fundamental

Simulated Resistor

-

- 회로의 저항 로 정의 가능

- Simulated Resistor의 저항과 별도 C가 결합된 회로(필터, Modulator 등)의 경우 frequency 의 오차가 1% 이내로 감소

728x90